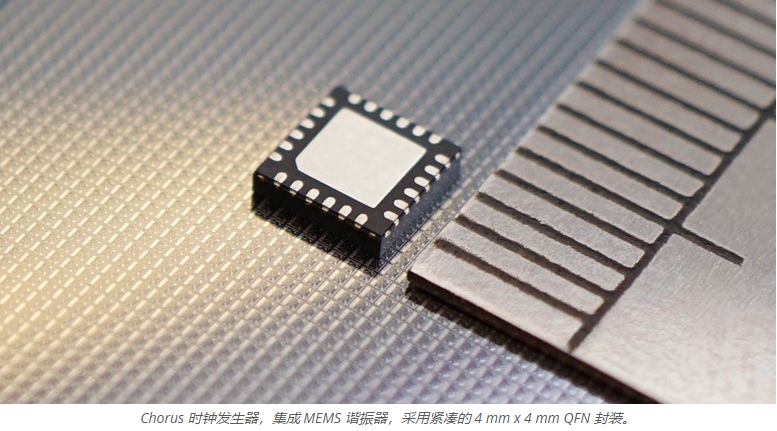

Chorus 时钟发生器首款面向 AI 数据中心的集成时钟

AI 已成为一种主流技术,几乎在一夜之间就拥有数百万用户。这种爆炸式增长推动了数据中心 AI 基础设施的快速部署,以及对高性能分布式计算和高带宽 400G/800G/1.6TB 网络设备的大规模升级需求。

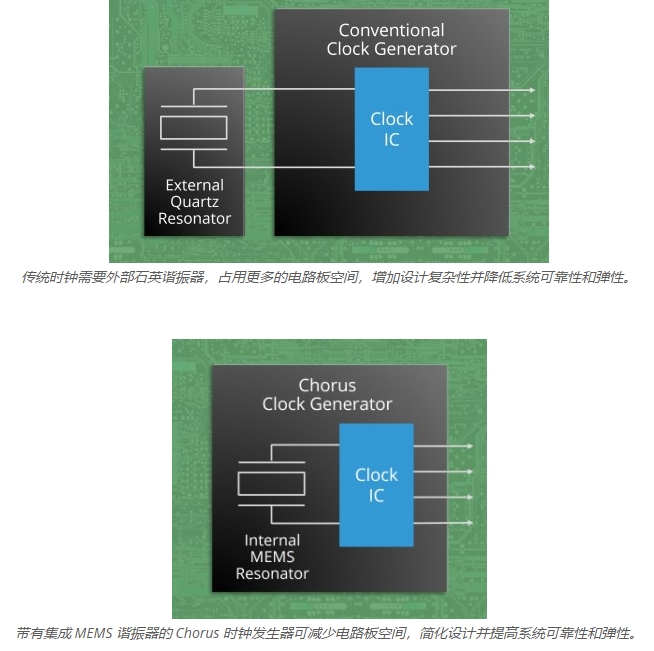

精确计时为 AI 基础设施提供检测信号。它在不同的 AI 工作负载之间提供必要的同步,以实现最大的 AI 服务器效率。精确的计时对于高速网络设备至关重要,该设备需要将大量数据传输到用于基于大型语言模型 (LLM) 的 AI 训练的服务器。为了满足 AI 带来的对更高性能和更高带宽的日益增长的需求,计时技术必须以同样快的速度进行创新。SiTime晶振的最新创新是基于 MEMS 的 Chorus™ 时钟片上系统 (ClkSoC),是第一款用于 AI 数据中心应用的集成时钟发生器。Chorus ClkSoC 将时钟 IC、硅 MEMS 谐振器和振荡器电路集成到单个芯片中。通过集成谐振器并消除对外部石英晶体器件的需求,Chorus 简化了系统时钟架构,将设计时间缩短了六周,并提高了可靠性和弹性。Chorus 时钟经过精心设计,性能提高了 10 倍,而尺寸仅为同等石英器件的一半。

Chorus 重新定义了 AI 数据中心等的时钟技术

Chorus 时钟发生器系列专为当今的通信和网络基础设施设备而设计。它将 MEMS 时序技术的优势引入 AI、数据中心、内核/边缘/接入网络应用等等。Chorus 时钟同样非常适合其他高可靠性应用,例如广播系统、测试仪器和电网基础设施。

Chorus 解决了传统 clock generator 的限制和设计难题。到目前为止,传统的 clock devices 通常依赖于外部石英晶体谐振器或振荡器来为锁相环 (PLL) 提供输入时钟参考。然而,在印刷电路板 (PCB) 上使用外部石英定时器件会暴露敏感的模拟节点,这些节点为 EMI 和电路板噪声耦合到振荡电路中提供了一条路径。必须确保正确的 PCB 设计,以最大限度地减少这种耦合并防止干扰。这需要额外的测试和设计周期。电路板噪声并不是使用石英器件的唯一危险。来自风扇和其他环境压力源的机械冲击或振动会降低晶体性能并影响时序稳定性。

此外,对于传统的 clock generator,设计人员必须选择与晶体的特定特性相匹配的正确负载电容,即使来自同一制造商,该特性也可能有所不同。负载电容匹配对于确保 clock 在整个温度范围内稳定、可靠的运行至关重要。但问题是:外部晶体和电容器会占用额外的电路板空间,并可能推高成本,更不用说管理这些电容器的供应链的麻烦了。

Chorus 时钟生成器架构的关键元素包括:

1、集成 MEMS谐振器,可消除外部石英的问题,例如电容失配、活动下降、易受冲击、振动和 EMI 的影响

2、完全可编程的低噪声 PLL

3、四个完全可编程的时钟输出,每个输出都有自己的专用电源

4、片上存储器,支持多种配置以解决原位时钟树变化

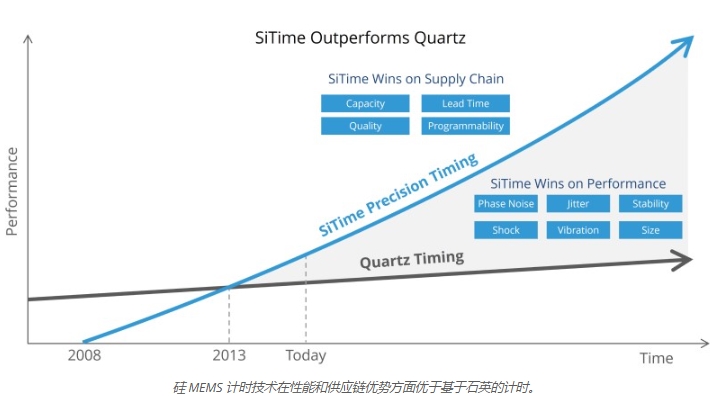

SiTime 久经考验的 MEMS 技术优于石英

通过集成 MEMS 谐振器,Chorus 时钟发生器为基于石英的计时技术提供了更好的替代方案:1、可靠性提高 10 倍,消除了与 Quartz 相关的性能和可靠性问题,包括现场故障

2、对电源噪声、EMI、冲击、振动和电路板弯曲的适应能力提高 10 倍

3、通过替换多达四个独立振荡器,PCB 上的时序占用空间减少 50%

1、空白在系统可编程 (ISP) 器件提供最大的设计灵活性和库存管理。

2、预编程器件无需软件配置即可启动系统,从而简化和加速设计和制造过程。

客户可以直接从 SiTime 订购完全配置的 Chorus 时钟,也可以选择空白(未配置)部件以获得更大的灵活性。SiTime 最先进的时序配置器工具使开发人员能够在评估或产品开发期间配置空白部件。该工具还可用于通过在器件的片上存储器中烧录全新的配置来重新配置已配置的 Chorus clock generator。

实现更智能、更快速的系统设计

Chorus 系列是新一代基于 MEMS 的时钟发生器,通过消除传统时钟 + 石英振荡器解决方案的设计复杂性并减少性能和可靠性问题,实现更智能、更快速、更好的系统设计。是时候转向基于 MEMS 的时钟技术的未来了。

了解有关 Chorus 时钟生成器的更多信息:

SiT91211 – 1 至 700 MHz、低抖动、±20 至 ±50 ppm MEMS 时钟发生器

SiT91213 – 1 至 700 MHz、超低抖动、±20 至 ±50 ppm MEMS 时钟发生器

全球咨询热线

全球咨询热线 手机端

手机端

亿金公众号

亿金公众号 亿金微信号

亿金微信号