使用HCMOS振荡器的源阻抗端接建议

HCMOS 端接

通常,接收器的 HCMOS 兼容输入显示高输入电阻与小引脚输入电容并联。接收器侧不接受终端电阻,因为 HCMOS 接收器输入需要轨到轨摆幅才能正确检测“H”和“L”电平。在传输线的接收器端添加一个 termination resistor 会减小 clock 信号摆幅,并且接收器的 input 信号可能不再满足所需的阈值电平。然而,接收器侧传输线的准开路端将导致信号反射,这些反射会传回发射器,即振荡器的缓冲器输出级。这就是为什么建议在发射器侧(即振荡器的输出)进行阻抗匹配,以避免已经在接收器侧反射的脉冲进一步反射。通过这种端接方法,波形不会退化,并且将满足 HCMOS 接收器所需的标准波形。CMOS (HCMOS和LVCMOS)是适合低频时钟晶振 (通常低于250MHz)的方波数字输出,可实现在时钟输出和芯片输入之间直接连接。 在大多数情况下,可以使用低值串联电阻器来有效减少信号反馈并保持可靠的信号完整性。

时钟脉冲及其频谱内容

首先,重要的是要了解阻抗匹配的需求不取决于 clock frequency 本身,而是取决于沿 PCB 走线移动的信号边沿的上升和下降时间。事实上,非常快的 rising 和 falling edges 将导致 oscillators clock frequency 倍数的高频 spectral content 。这种高频频谱内容是由高次谐波引起的,这些谐波包含在 clock output 信号的几乎矩形波形中。

如果信号走线的长度接近 clock 信号的光谱内容内最高频率的波长 λ,就会发生所谓的脉冲反射。由于高频频谱内容取决于 clock 信号的上升和下降时间,因此可以根据振荡器 clock output的指定上升和下降时间来估计 PCB 走线的临界长度。CMOS (HCMOS和LVCMOS)通常为普通有源晶振输出逻辑,包括压控晶振(VCXO)及压控温补晶振 (VC-TCXO)等。

临界波长 λ

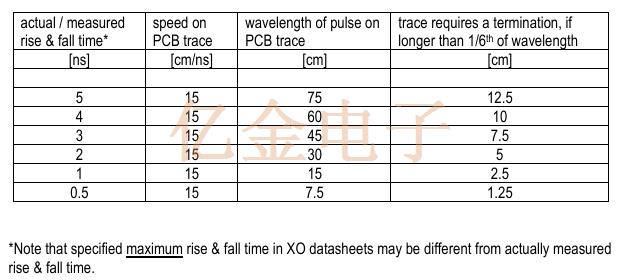

根据经验,我们可以说 signal trace 的临界长度应该比占 clock 信号上升沿或下降沿持续时间的谐波分量的波长 λ 短 6 倍。要计算波长 λ,我们必须考虑信号边沿在传输线上的传播速度。

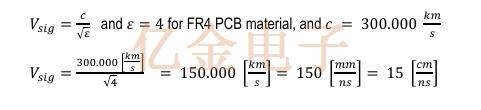

沿传输线的传播速度由 PCB 基材决定。对于 εε=4 的 FR4 PCB 材料,传播速度 VSig 可以估算如下:

对 PCB 设计的影响

假设信号轨迹的长度短于在该轨迹上传播的快速脉冲波长的1/6,那么如果上升和下降时间在电压摆动的10%~90%给出,我们可以估计轨迹的关键长度与时钟信号的上升和下降时间的关系。如果上升和下降时间规定为电压摆幅的 20% 和 80%,则基于 1/4 波长的计算是可以接受的。

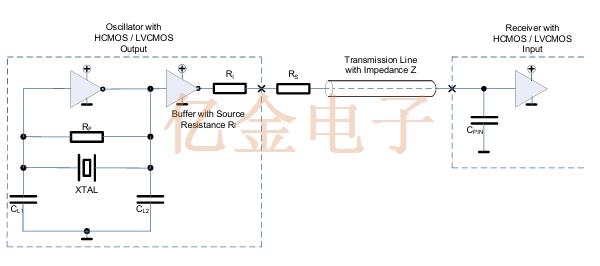

源阻抗终端

由于不允许在接收器端接,因此建议在石英晶体振荡器输出和传输线之间进行阻抗匹配,以避免反射在 PCB 走线的两个方向上传播。假设振荡器的输出具有源阻抗 RI,并且传输线具有高于 RI 的特性阻抗 Z,则应增加一个串联电阻 RS。为了实现最佳阻抗匹配,RI 和 RS 之和应等于特性阻抗 Z。RS 的最佳值可以通过实验确定,尤其是在 PCB 走线的阻抗 Z 未知的情况下。

如果使用具有 HCMOS 输出的32.768K振荡器,则应将串联电阻 RS 放置在非常靠近振荡器输出的位置。源阻抗 RI 和串联电阻 RS 之和应等于传输线的阻抗 Z。

这种推荐配置的目的是避免在传输线的接收器端反射的脉冲进一步反射。通常,不建议在接收器侧使用 termination resistor,因为它们会降低 clock 信号的电压摆幅,并且可能无法再达到接收器侧所需的阈值电平。

全球咨询热线

全球咨询热线 手机端

手机端

亿金公众号

亿金公众号 亿金微信号

亿金微信号