HCMOS晶体振荡器面临的挑战

当使用具有 HCMOS 兼容输出信号的石英晶体振荡器时,可能会出现阻抗失配。当低源阻抗输出用于驱动具有较高阻抗的 PCB 走线时,就会发生这种情况。这可能会导致 clock 信号中出现 noise。因此,建议对 HCMOS 电路匹配振荡器输出和传输线之间的阻抗。

本文档描述了 HCMOS 晶体振荡器面临的挑战,并展示了确保 clock 信号无干扰的可能配置方法。

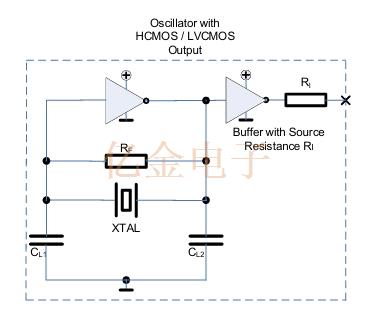

频率范围低于 150 MHz 的大多数振荡器都提供单端 HCMOS 或 LVCMOS 兼容输出,具有轨到轨输出摆幅。首字母缩略词 CMOS 来自 Complementary Metal Oxide Semiconductor,这意味着振荡器的输出缓冲器由互补的 p 沟道和 n 沟道 MOS 晶体管构建。

理想情况下,振荡器的 output buffer 可以看作是一个可以在 rail-to-rail 之间摆动的输出级。然而,由 MOS 晶体管构建的实际输出级会出现一些损耗,这些损耗由具有低阻抗的源电阻 RI 表示。

1. 问题

每当使用具有较低源阻抗的 HCMOS 输出缓冲器来驱动 PCB 时钟走线上具有较高阻抗的负载时,就会发生阻抗不匹配。根据应用和 PCB 布局,这种阻抗不匹配会导致负载发生电压反射,这可能会在 clock waveform 中产生阶跃或毛刺、振铃以及过冲和下冲。这种降级的波形会降低接收器端的时钟信号质量,导致数据出现错误时钟并产生不需要的触发,从而导致系统性能不佳。有源晶振可HCMOS/TTL兼容、ACMOS兼容、ECL和正弦波输出,每种输出类型都有它的独特波形特性和用途。

2. 终止原因

SPXO石英晶振较长的 clock traces 不能再简化为 lumped trace。实际上,必须将 PCB 上较长的 clock trace 视为传输线,这意味着 clock signal edges 以快速传播速度沿着 PCB 走线传播。

如果 PCB 走线的长度超过一定限制,则需要匹配传输线阻抗。根据信号标准,阻抗匹配在接收器侧、的输出通常会在 PCB 上馈送一条走线,只有当它足够短时,才能将其视为简单的连接。然而,PCB 上发射器侧甚至两侧进行。通常,终端电阻器用于阻抗匹配。最好在传输线的两端进行阻抗匹配,以避免两端的反射。但是,在 HCMOS 电路中,不允许在接收器侧进行端接。

3. HCMOS 端接

通常,接收器的 HCMOS 兼容输入显示高输入电阻与小引脚输入电容并联。接收器侧不接受终端电阻,因为 HCMOS 接收器输入需要轨到轨摆幅才能正确检测“H”和“L”电平。在传输线的接收器端添加一个 termination resistor 会减小 clock 信号摆幅,并且接收器的 input 信号可能不再满足所需的阈值电平。然而,接收器侧传输线的准开路端将导致信号反射,这些反射会传回发射器,即振荡器的缓冲器输出级。这就是为什么建议在发射器侧(即振荡器的输出)进行阻抗匹配,以避免已经在接收器侧反射的脉冲进一步反射。通过这种端接方法,波形不会退化,并且将满足 HCMOS 接收器所需的标准波形。CMOS (HCMOS和LVCMOS)是适合低频时钟晶振 (通常低于250MHz)的方波数字输出,可实现在时钟输出和芯片输入之间直接连接。 在大多数情况下,可以使用低值串联电阻器来有效减少信号反馈并保持可靠的信号完整性。

全球咨询热线

全球咨询热线 手机端

手机端

亿金公众号

亿金公众号 亿金微信号

亿金微信号