面向 FPGA 设计人员的精密时序解决方案

FPGA 的精确时序

面向 FPGA 设计人员的精密时序解决方案 关键考虑因素FPGA 已经远远超越了由逻辑和触发器组成的原始内核架构,周围环绕着通用 I/O。该结构已升级为嵌入式存储器、DSP 模块、AI 处理器,所有这些都通过片上网络连接。除了升级的结构外,FPGA 现在还配备了多核处理器。I/O 环还升级了一系列硬核 IP 块和高速 SerDes,以支持多种接口,如千兆以太网、PCIe、DRR 内存等。当今的现代 FPGA 已成为具有复杂时钟要求的可编程 SoC。

FPGA 代表一个复杂的时钟环境

随着 FPGAs 功能的增加,clocking 需求的复杂性也随之增加。因此, FPGA 供应商添加了几个 built-in PLLs 和 clock management 功能。这种功能的增加反映在所需时钟源的增加上:

1、嵌入式 PLL 的多个参考时钟

2、每个 I/O bank 参考时钟

3、用户逻辑的时钟

4、用于实时时钟、配置控制器等功能的各种支持时钟源。

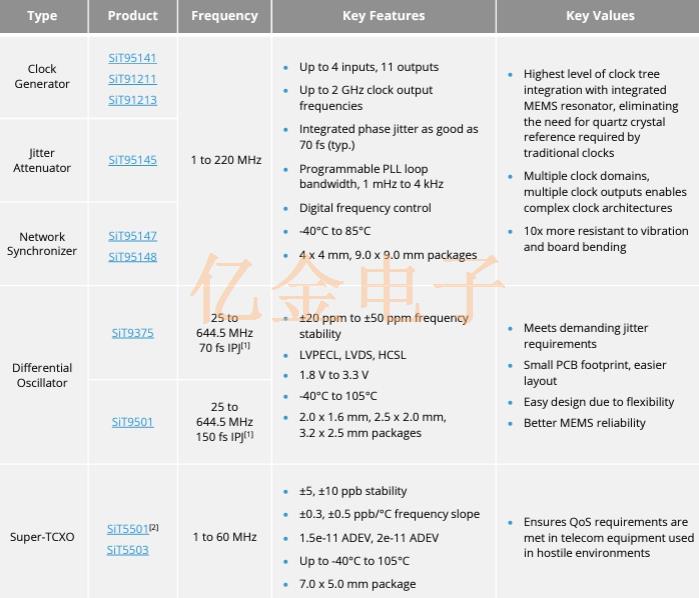

对于基于 SRAM的 FPGA,可能需要额外的 external logic 来控制配置。通常使用较小的 CPU 和 flash memory,需要自己的 clock source。这些 FPGAs 和支持 configuration logic 并不孤立地存在于电路板上。例如,可以找到与 FPGA 结合使用的高端 CPU,FPGA 充当 CPU 的硬件加速器。通常可以在电路板上找到其他设备,如收发器、DRAM 和其他 ASSP。所有这些器件都有自己的 clocking 要求,共同创建了一个复杂的 clocking 环境。设计人员需要一个能够提供从石英振荡器到时钟管理器件的一系列时钟解决方案的供应商。

FPGA 无处不在

FPGA 时钟晶振是一种小众产品,无处不在,从机顶盒到 GPS 制导弹药,从海底到太空 - 任何需要定制解决方案的地方。但是,定制 ASIC 的成本高昂(从 NRE 的角度来看),或者无法满足上市时间需求。因此,FPGA 设计人员需要一家供应商,其产品线支持从办公室的良性条件到温度范围宽、振动和压力大的恶劣环境。

为什么选择 SiTime 晶振定时解决方案

一、在恶劣环境中更坚固

1、抗振性提高 4 倍 — 典型值为 0.1 ppb/g

2、抗冲击能力提高 20 倍

二、 在较宽的温度范围内具有更好的稳定性

1、工作温度高达 -55 至 +125°C

2、耐气流和热冲击 — 1 ppb/°C

三、高可靠性

1、质量和可靠性提高 50 倍

2、终身保修

四、 可编程性,设计灵活

1、任何频率,任何稳定性,宽范围内的任何电压

2、一次认证多个部件 独特的功能

3、EMI降低 - 降低30分贝

4、低功耗,电池寿命更长

5、100 kHz时为4.5 μA

6、更小的尺寸 - 1.5 mm x 0.8 mm封装

全球咨询热线

全球咨询热线 手机端

手机端

亿金公众号

亿金公众号 亿金微信号

亿金微信号