ECS Crystal成立至今已是国际有名的晶体频率元件制造商,所生产的石英晶体,SMD晶振,石英晶体振荡器具有高稳定性,低功耗等特点.ECS振荡器产品系列包括时钟振荡器,TCXO,VCXO,VCTCXO和VCXO.下面亿金电子ECS晶振代理商介绍有关ECS振荡器电路设计考虑因素的信息.

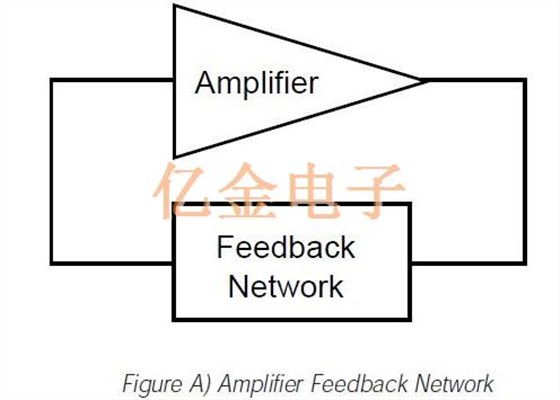

晶体控制振荡器可以被认为包括放大器和反馈网络,其选择放大器输出的一部分并将其返回到放大器输入.您可以在下面查看此类电路的示例.

(A)环路功率增益必须等于同步.

(B)环路相移必须等于0,2Pi,4Pi等弧度

反馈到放大器输入端的功率必须足以提供振荡器输出,放大器输入和克服电路损耗.

振荡器工作的确切频率取决于振荡器电路内的环路相位角度偏移.相位角的任何净修改都将导致输出频率的变化.作为振荡器提供基本上与变量无关的频率的通常目标,必须采用一些减少净相改变的方法.可以想象,最小化和最大限度地减少净相移的最常见方法是在反馈回路中使用石英晶体单元.

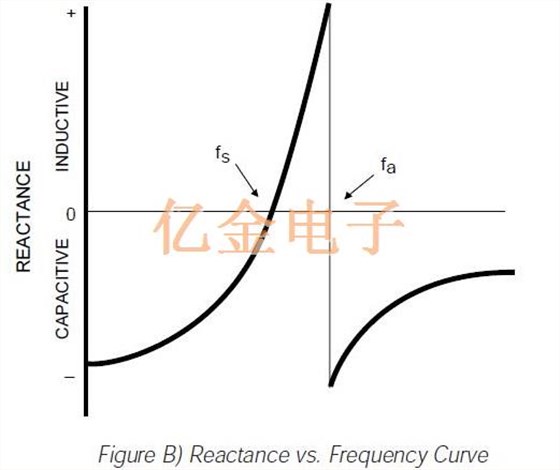

石英晶体的阻抗变化如此剧烈,随着施加频率的变化,所有其他电路元件可被认为是基本上连续的电抗.因此,当在振荡器的反馈回路中使用石英晶体单元时,晶体单元的频率将自我调节,使得晶体单元呈现满足环路相位必要性的电抗.以下显示石英晶体单元的电抗与频率的表示.

从图B中可以明显看出,石英晶体单元具有两个零相位频率.两者中的初始或较小的是串联谐振频率,通常缩写为Fs.零相位的两个频率中的后续或更高频率是相应的或反共振频率,通常缩写为Fa.串联和相应的谐振频率在振荡器电路中都是电阻性的.在串联谐振点处,电阻最小并且电流最大.

在平行点处,电阻是最大的并且电流是边际的.因此,并联谐振频率Fa永远不应用作振荡器电路的控制频率.

通过在振荡器电路的反馈回路中包括无功分量(通常是电容器),可以使石英晶体单元在沿串联和并联谐振点之间的线的任何点处振荡.因此,增加电容产生的频率高于串联谐振频率;它通常被称为并行频率,但它小于事实并行频率.

正如有两个与石英晶振单元相关的零相位频率,有两个主振荡器电路.这些电路通常由要使用的晶体单元的类型定义,即"串联"或"并联".

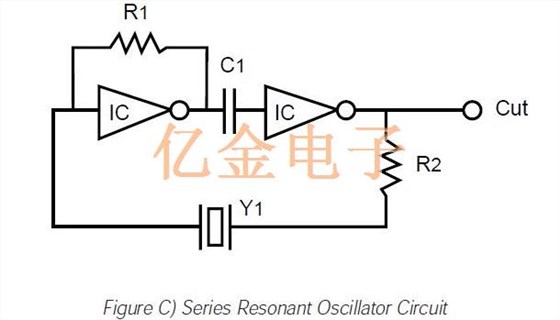

串联电路:串联谐振振荡器电路使用的晶体设计为以其自然串联谐振频率工作.在这样的电路中,反馈回路中不会有电容器.串联谐振振荡器电路的使用主要是因为它们的元件数量最少.尽管如此,这些电路可以提供除通过晶体单元之外的反馈路径.因此,在发生晶体故障时,这种电路可能保持以某些主观频率振荡.下面给出基本串联谐振振荡器电路的表示.

从图C中可以看出,如果需要修改,串联谐振振荡器电路不提供调节输出频率的手段.在上述电路中,利用电阻器R1来偏置逆变器并使其在其线性区域中工作.该电阻还向逆变器提供负反馈.电容器C1是连接器电容器,用于阻断直流电压.电阻器R2用于偏置晶体单元;因此,必须注意不要选择太小的值.晶体单元Y1是串联谐振晶体单元,被指定以优选频率工作并具有所需的频率容差和稳定性.

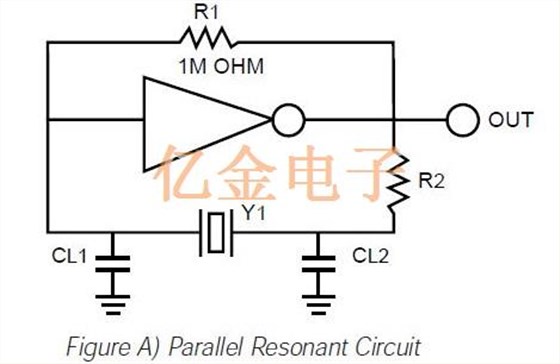

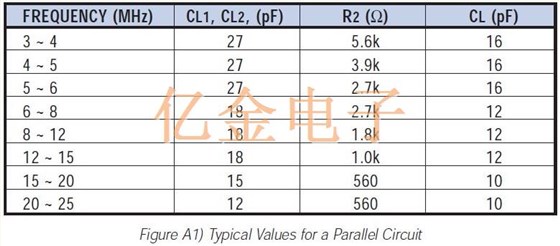

并联电路:并联谐振振荡器电路使用晶体单元,该单元设计用于以指定的负载电容值工作.这将产生一种结果,其中晶振晶体频率高于串联谐振频率但低于真正的并联谐振频率.这些电路不提供通过晶体单元以外的路径来完成反馈环路.在晶体单元发生故障时,电路将不再继续振荡.下面给出并联谐振电路的简单描述.

该电路使用单反相器,反馈环路中有两个电容.这些电容包含"负载电容",并与晶体单元一起产生振荡器工作的频率.随着负载电容值的改变,振荡器的输出频率也会改变.因此,如果需要调整,该电路确实提供了调整输出频率的合适方法.

该电路使用单反相器,反馈环路中有两个电容.这些电容包含"负载电容",并与晶体单元一起产生振荡器工作的频率.随着负载电容值的改变,振荡器的输出频率也会改变.因此,如果需要调整,该电路确实提供了调整输出频率的合适方法.

电阻器R1和R2的功能与图C所示的串联谐振电路的功能相同.两个负载电容CL1和CL2有助于确定晶振晶体单元和振荡器工作的频率.晶体单元Y1是并联谐振晶体单元,规定以优选频率和所需频率容差和稳定性以指定的负载电容值工作.

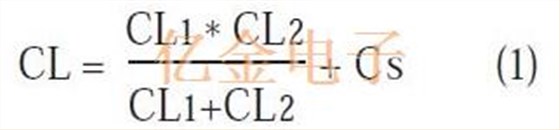

负载电容:已参考"指定负载电容".负载电容可以描述为"通过晶体的连接点存在于振荡器电路中的电容的值,测量或计算的".在串联谐振电路的情况下,晶体单元的连接点之间不存在电容,因此,对于串联谐振晶体单元,不需要说明负载电容.在并联谐振振荡器电路的情况下,存在电容.由于该电容的直接尺寸是不合理的,因此经常需要计算该值.负载电容值的计算通过以下等式完成:

其中CL1和CL2是负载电容,Cs是电路流浪电容,通常为3.0到5.0pF.

必须注意的是,负载电容值的变化将导致振荡器输出频率的变化.因此,需要精确的频率控制,然后需要精确的负载电容规范.为了演示,假设石英贴片晶振单元被指定在20.000MHz的频率下工作,容量为20.0pF.假设晶体单元然后放置在一个评估为30.0pF的电路中.然后,晶体单元的频率将低于指定值.相反,如果有关电路的评估值为10.0pF;频率将高于指定值.负载电容之间的关联如下所示.

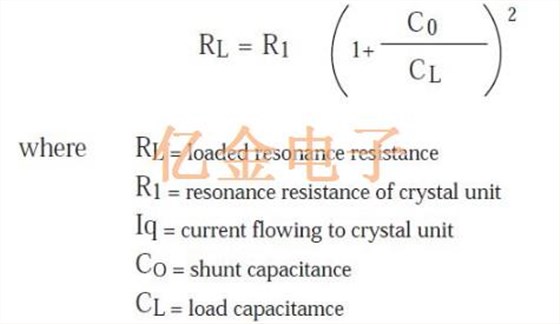

DRIVE LEVEL:"驱动电平"是晶体单元在工作时消耗的功率.功率是所施加电流的函数,通常用毫瓦或微瓦表示.晶体单元被指定为具有某些驱动电平的最大值,其作为频率和操作模式的函数进行变换.最好与晶体单元供应商商讨特定晶体单元允许的驱动电平的最大值.超过给定晶体单元的最高驱动水平可能导致不稳定的操作放大老化速率,并且在某些情况下,导致灾难性破坏.驱动电平可以通过以下等式计算:

其中"I"是通过晶体单元的均方根电流,R是所讨论的特定晶体单元的最大电阻值.等式(2)简单地说就是"欧姆定律".

可以通过临时插入与晶体单元串联的电阻器来完成操作振荡器电路中的实际驱动电平的测量.电阻必须与石英晶体单元具有相同的欧姆值.然后可以读取电阻器两端的电压降,并计算电流和功耗.然后必须移除电阻器.作为测量驱动电平的替代方法,可以在空间允许的情况下在晶体单元的输出引线处使用电流探针.该方法在下面的图1中描述.

频率与模式:石英晶体单元的频率受振动石英元件的物理尺寸限制.在某些情况下,限制尺寸是长度和宽度.在最流行的晶体单元"AT"切割晶体单元的情况下,限制尺寸是振动石英元件的厚度.随着厚度减小,频率增加.在通常约30.000MHz的某些点处,石英板的厚度变得太薄而不能加工.

如果需要开发频率高于极限频率的石英晶体振荡器,必须考虑到石英晶体单元将以其"基本"频率的奇数倍振荡的事实.我们可以将"基本"频率定义为"在给定的一组机械尺寸上自然发生的频率".因此,如果晶体单元的基频为10.0MHz,也可以使其在基波的3,5,7等时振荡.也就是说,该单位将在30.0振荡.50.0,70.0等MHz

这些基频的倍数称为"泛音",由乘法的整数表示,如"三次泛音","五次泛音"等.当需要使用泛音频率时,晶体单位必须是指定以期望的频率和期望的泛音操作.人们不应该尝试订购基模晶体,然后以泛音频率进行操作.这是因为晶体制造工艺对于基本和泛音晶体单元而言是不同的.

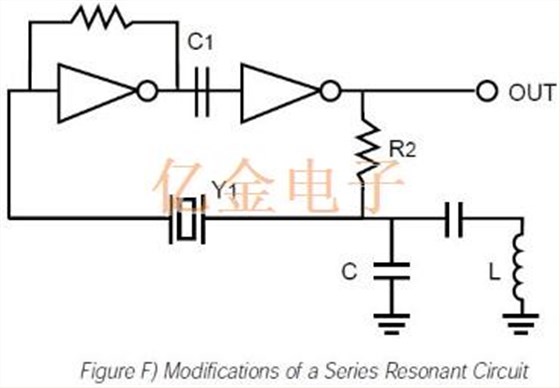

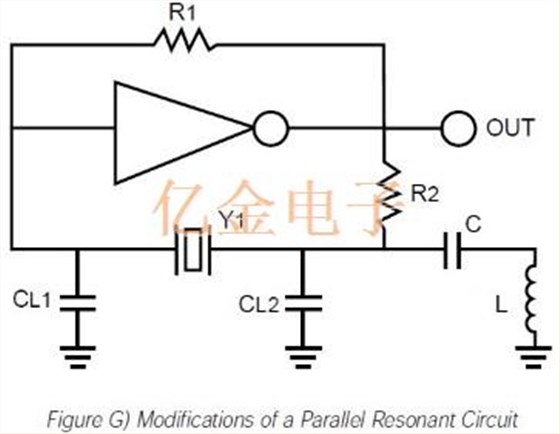

在许多情况下,在特定振荡器设计中使用的集成电路的特性决定了地壳单元的基频被抑制,以确保在所需频率和期望的泛音下操作.在这种情况下,通常需要修改振荡器电路.一种修改方法是添加"槽"电路,包括电感器和电容器.这些修改如图F和G所示.

在这两种情况下,谐振电路都转向在基频和所需频率之间的某个频率下谐振.这导致不需要的频率被分流到地,在振荡器的输出端仅留下所需的频率.

设计考虑因素:为了振荡器电路的良好运行,应遵循某些设计考虑因素.在所有情况下,建议避免使用并行走线,以减少电路杂散电容.所有迹线应尽可能短,并应隔离组件以防止耦合.应使用地平面隔离信号.

负阻力:为了获得最佳性能,必须设计振荡器电路以增强"负电阻",有时称为"振荡裕量".通过临时安装与ECS石英晶体振荡器晶体单元串联的可变电阻器来实现对给定电路中的负电阻量的评估.电阻应初始设置为最低设置,最好接近零欧姆.启动振荡器并在示波器上监视输出.然后调节可变电阻器,以便在连续监测输出的同时增加电阻.在一定的电阻值下,振荡将停止.此时,测量可变电阻器以确定振荡停止的欧姆值.对于这个值,晶体单元的最大电阻,必须添加供应商指定的.总欧姆电阻被认为是"负电阻"或"振荡裕量".为了获得良好,可靠的电路操作,建议负电阻至少为晶体单元规定的最大电阻值的五倍.

负电阻值超过晶体单元最大电阻的五倍是更好的.由于负电阻在高温下趋于降低,因此建议在工作范围的最高温度下进行测试.请参阅下面说明的特殊程序.

负阻测量程序

1)打开所用主电路中晶体单元的任一端,并插入一个与晶体振荡器单元串联的可变电阻,如图所示.改变电阻值以检查当时观察到的振荡极限和电阻(欧姆).在这种情况下,必须打开和关闭电源,确保无误.

2)电路中的负电阻(-R)是上述步骤1)获得的值与晶体的谐振电阻R1之和.

注意:该测量应在工作温度范围的上限和下限进行.

3)C1和C2应在10~30pF的范围内使用.如果C1和C2的使用低于10pF或高于30pF,则振荡性能可能很容易受到影响.驱动电平可能会增加,或负电阻可能会降低,从而无法保持振荡.

SMI晶振,86M0368 -16,86SMX进口晶振,6G相关设备晶振

SMI晶振,86M0368 -16,86SMX进口晶振,6G相关设备晶振 日本SMI晶体,53SMX石英晶振,53M320-16,6G基站晶振

日本SMI晶体,53SMX石英晶振,53M320-16,6G基站晶振